Registros de turno puede clasificarse en dos tipos, a saber, registros de cambio estático y Registros de cambio dinámico. Los registros de desplazamiento estático se componen de flip-flopy son capaces de almacenar la información dentro de ellos por un período de tiempo indefinido. Por otra parte, los registros de cambio dinámico están formados por inversores dinámicos y emplean técnicas de almacenamiento de carga temporal, por lo que requieren ciclos de actualización frecuentes para almacenar los datos.

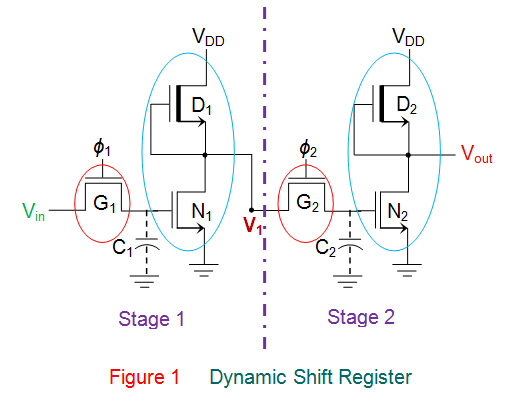

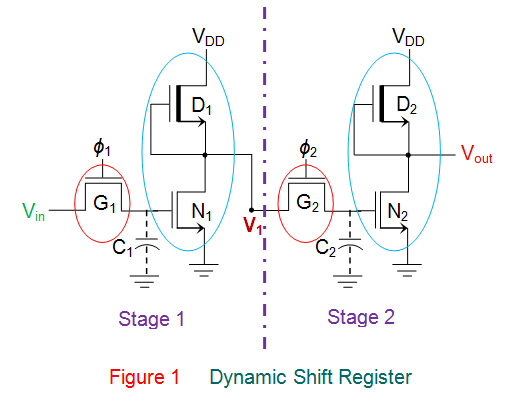

La figura 1 muestra un registro de desplazamiento dinámico formado por una combinación de puertas de transmisión NMOS (componentes en círculo rojo, G1 y G2) e inversores de modo de agotamiento NMOS (componentes con círculos azules, {D1, N1} y {D2, N2}). Aquí1 y2 son señales de reloj no superpuestas y mutuamente complementarias, mientras que C1 y C2 representan las capacitancias de la puerta a la fuente de la Etapa 1 y la Etapa 2, respectivamente. Además, estas capacitancias se consideran agotadas en su estado inicial.

Ahora considera que Ven = 0V y1 = VDDque corresponden a los estados lógicos 0 y 1 respectivamente. Para este caso, la puerta G1 será abierto (no conductor) y por lo tanto el condensador C1 permanecerá en su estado sin carga.

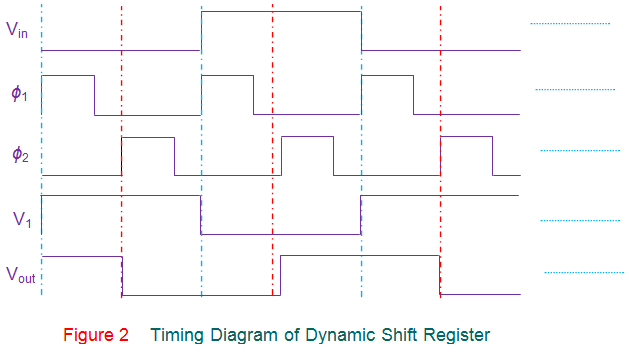

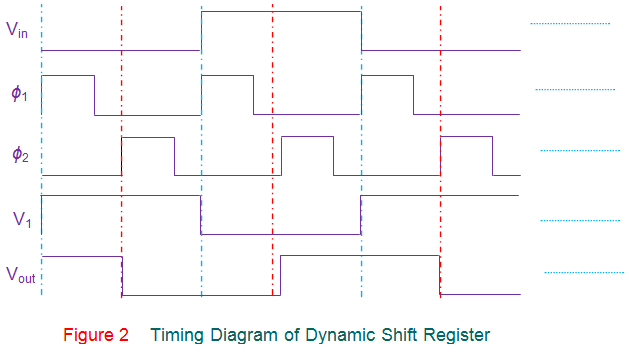

Esto causa que la salida voltaje nivel del circuito inversor en la Etapa 1 (formado por D1 y N1) para ir alto i.e. V1 = VDD (asumiendo un voltaje de umbral cero para todos los dispositivos del circuito sólo por simplicidad). Sin embargo, para esto,1 debe mantenerse en su estado elevado durante un tiempo suficiente, ya que la carga del condensador es un proceso gradual (considerando la emisión constante de tiempo RC). Ahora bien, si2 va alto y luego la puerta G2 se cierra debido a que el condensador C2 comienza a cargarse a través de él gradualmente hasta el nivel de voltaje de VDD (= V1), imponiendo las restricciones a la frecuencia del reloj en uso. Además, hay que señalar que como el voltaje a través del condensador C2 aumenta, el voltaje de salida en la Etapa 2 disminuye debido a la acción inversora del circuito formado por D2 y N2. Esto a su vez causa que el voltaje de salida, Vfuera …para que baje (= 0V). Por lo tanto, se puede decir que el estado de Ven se desplaza a Vfuera.

De manera similar, si Ven = VDD mientras que1 = VDDy luego C…1 cargos a VDD a través de G1 causando que el voltaje de salida de la Etapa 1, V1 …para ir a lo más bajo. En este instante si2 = VDDy luego la puerta G.2 se cierra, el condensador C2 se descarga mientras que el voltaje de salida, Vfuera aumenta gradualmente. Así se obtiene Vfuera = VDDreflejando el alto estado lógico de entrada voltaje. Por lo tanto, una vez más, el estado de Ven se refleja en Vfueralo que implica que la Ven se desplaza a Vfuera bajo el control del reloj. Esto significa que el circuito que se muestra en la figura 1 actúa como un registro de desplazamiento de una sola etapa. Sin embargo, un registro de cambio dinámico de n etapas puede ser diseñado por la cascada de n número de tales etapas.

El funcionamiento de la etapa única registro de cambio dinámico se puede enfatizar aún más con el diagrama de tiempos que se muestra en la figura 2.

De la explicación se desprende claramente que los registros de cambio dinámico almacenan la información en forma de carga en la capacitancia parásita de puerta a sustrato de los dispositivos electrónicos (especialmente MOS). Sin embargo, esta carga es propensa a las fugas y, por lo tanto, es necesario refrescar los datos periódicamente para garantizar que los niveles lógicos de los datos almacenados estén libres de errores. Este objetivo se logra desplazando continuamente los datos de una etapa a otra mientras se retroalimenta la salida de la última etapa a la primera. Esto significa que los registros de desplazamiento dinámico deben funcionar a la mínima frecuencia de reloj.

Registros de cambio dinámico son más simples en términos de fabricación y tienen una alta densidad de paquetes debido a su menor tamaño. Sin embargo, cabe señalar que su ventaja de menor consumo de energía está maldita por el hecho de que la energía consumida aumenta con el aumento de la frecuencia. Además, hay muchas variaciones de diseño disponibles en el caso de los registros de cambio dinámico, como los registros de cambio dinámico que utilizan la carga de mejora, los registros de cambio dinámico que utilizan dispositivos CMOS y así sucesivamente, incluyendo el enfoque de lógica proporcional y el enfoque de lógica menos proporcional. No obstante, el principio básico de funcionamiento sigue siendo el mismo.